创建时间:2025-12-25 10:41:36

在PCB设计与制造领域中,短路故障无疑是工程师和制造商最头疼的“头号杀手”。然而PCB设计导致的短路究竟如何产生?短路是否能在设计阶段被检测出来?设计时如何系统性预防?本文告诉你答案。

一、探本溯源:PCB设计阶段埋下的雷

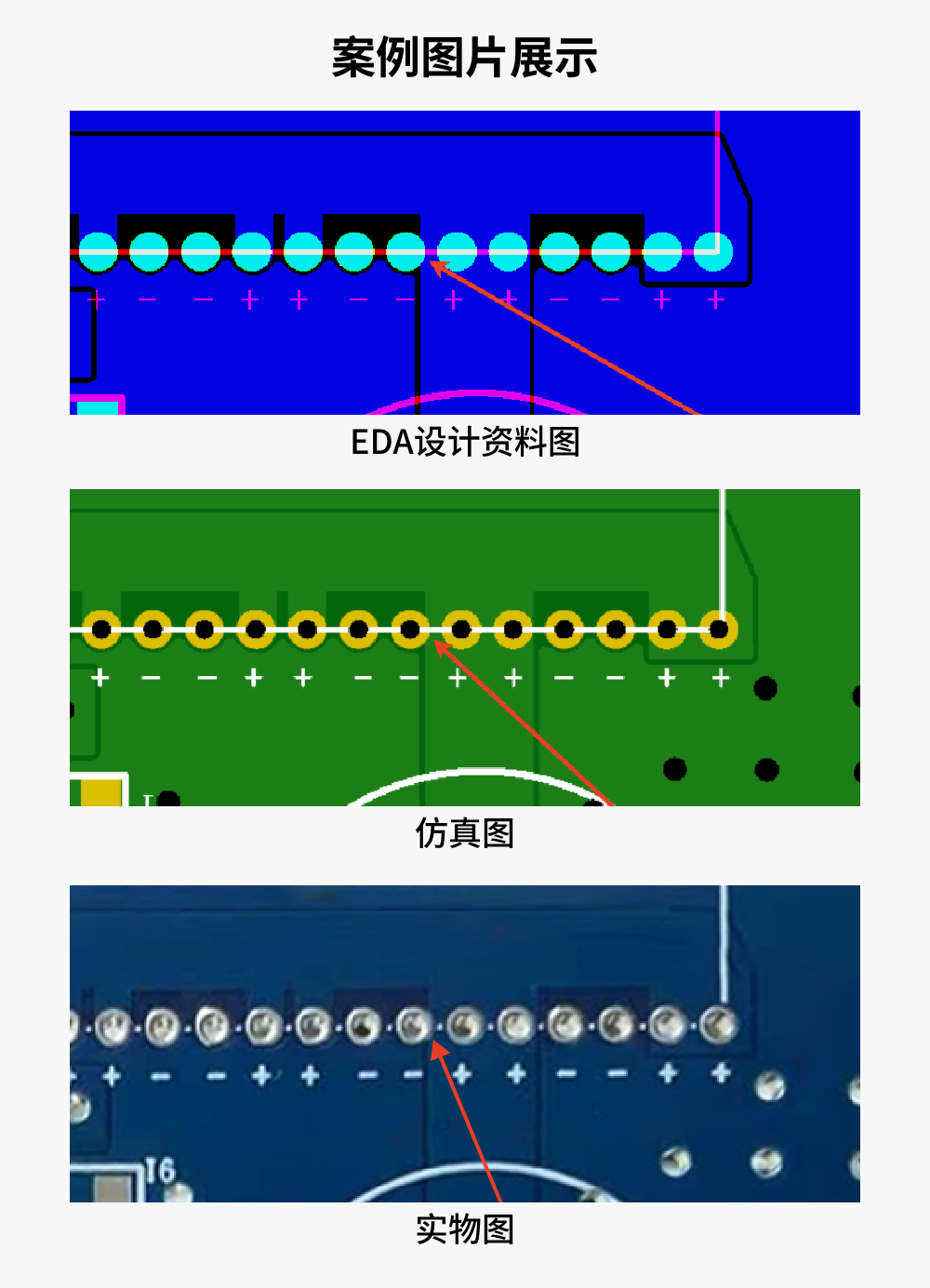

案例一:不同网络铜皮导通

案例解释:左侧孔在第二层与电源(-) 网络连接,而右侧孔网络属性是电源(+) ,并采用了手动铺铜的方式进行走线,因此电源(+) 与电源(-) 区域发生重叠导致短路。

问题根源:

1)未针对电源(+) 与电源(-) 网络设置差异化安全间距规则。

2)手动铺铜时电源(+) 网络的铜皮误覆盖至电源(-) 网络上。

对于手动铺铜时因操作失误导致不同网络(如电源与地)意外相连的情况,主流EDA工具(如Altium Designer, Cadence, PADS, 嘉立创EDA)一般会根据设计规则(DRC)进行报错。

但在某些特定设置或操作下,这类问题确实可能被遗漏,从而不产生报错:

1)使用错误的铺铜对象,使用“实心填充 (Fill) ”而非“智能铺铜 (Polygon Pour) ”,前者会无条件连接覆盖区域内所有对象,可能导致短路而DRC不会报错。

2)设计规则 (DRC) 设置不当或未开启“在线DRC”检查,规则中的间距 (Clearance) 值设置过小,使短路间隙未被识别为违规。

3)使用非电气对象,错误地使用2D线段代替导线进行连接,这些对象没有网络属性,DRC无法检查,可能导致输出Gerber时短路。

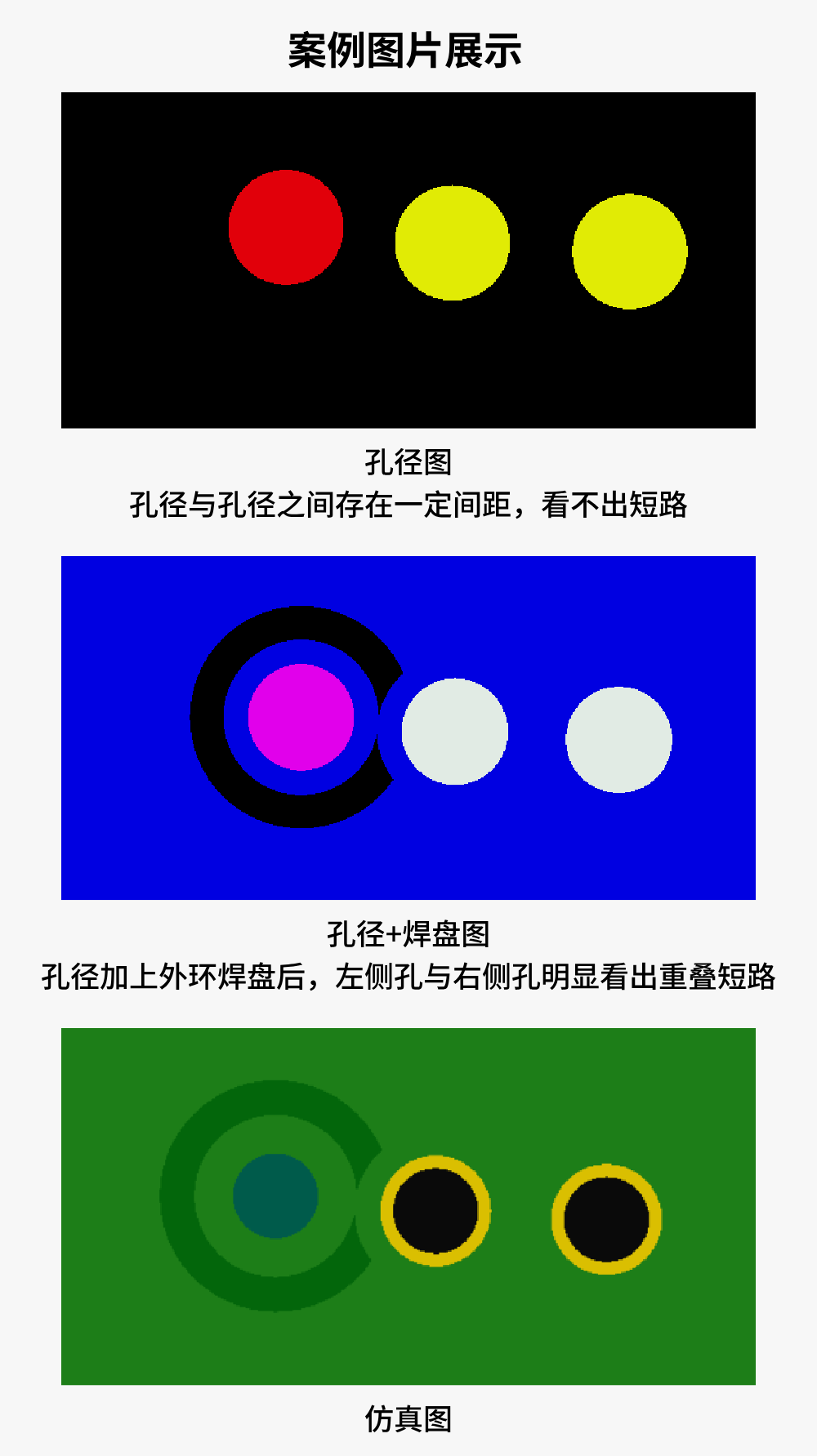

案例二:不同网络过孔重叠

问题根源:左侧过孔在Bottom层与GND网络连接,中间过孔在Top层与于VCC网络连接,两孔孔壁位置重叠,导致电源与地通过孔壁直接短路。

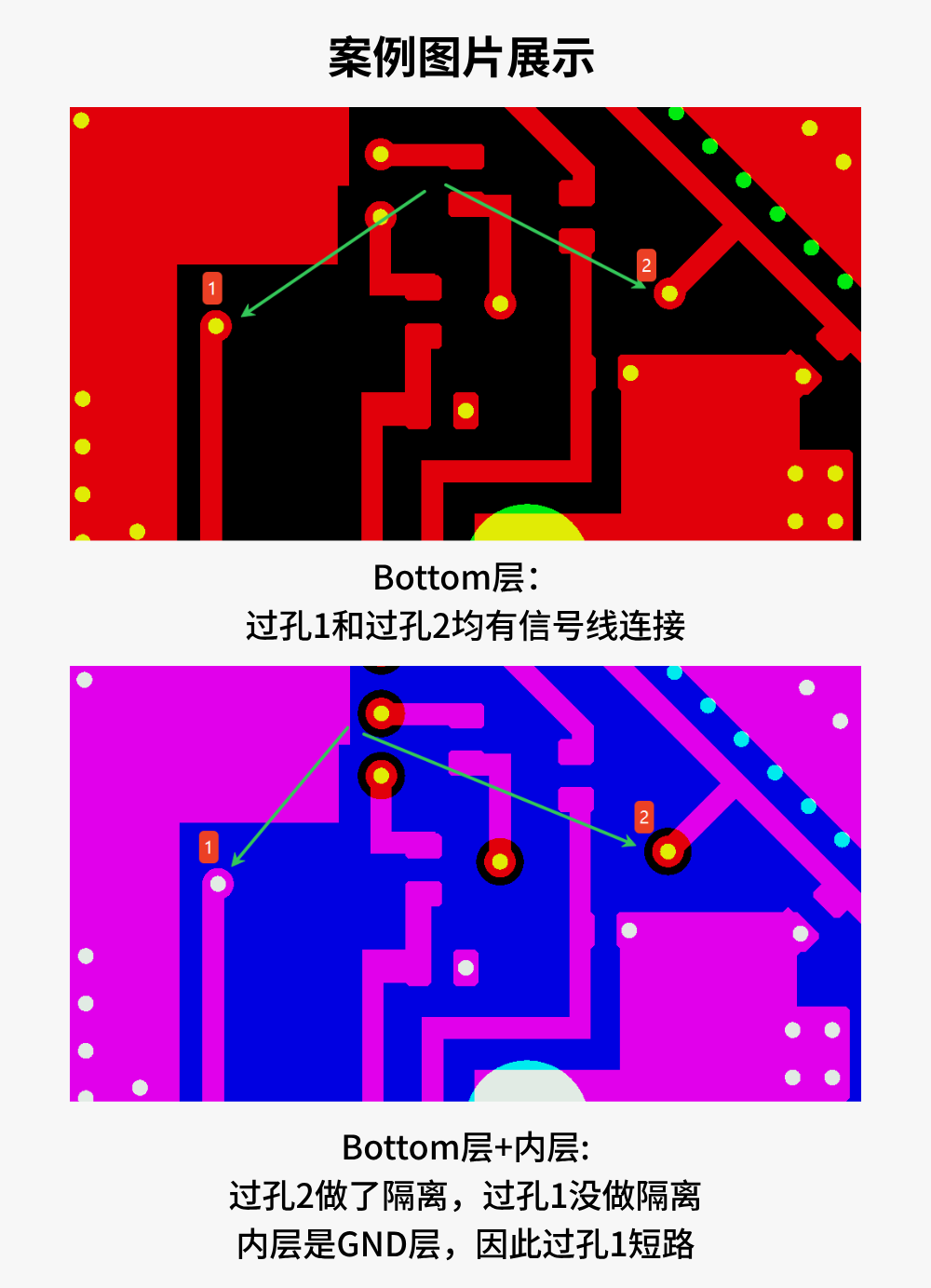

案例三:中间层隔离缺失

问题根源:过孔连接不同板层(1、4层),但中间层(2、3层)未做隔离,导致过孔与中间层非同源网络铜皮导通。

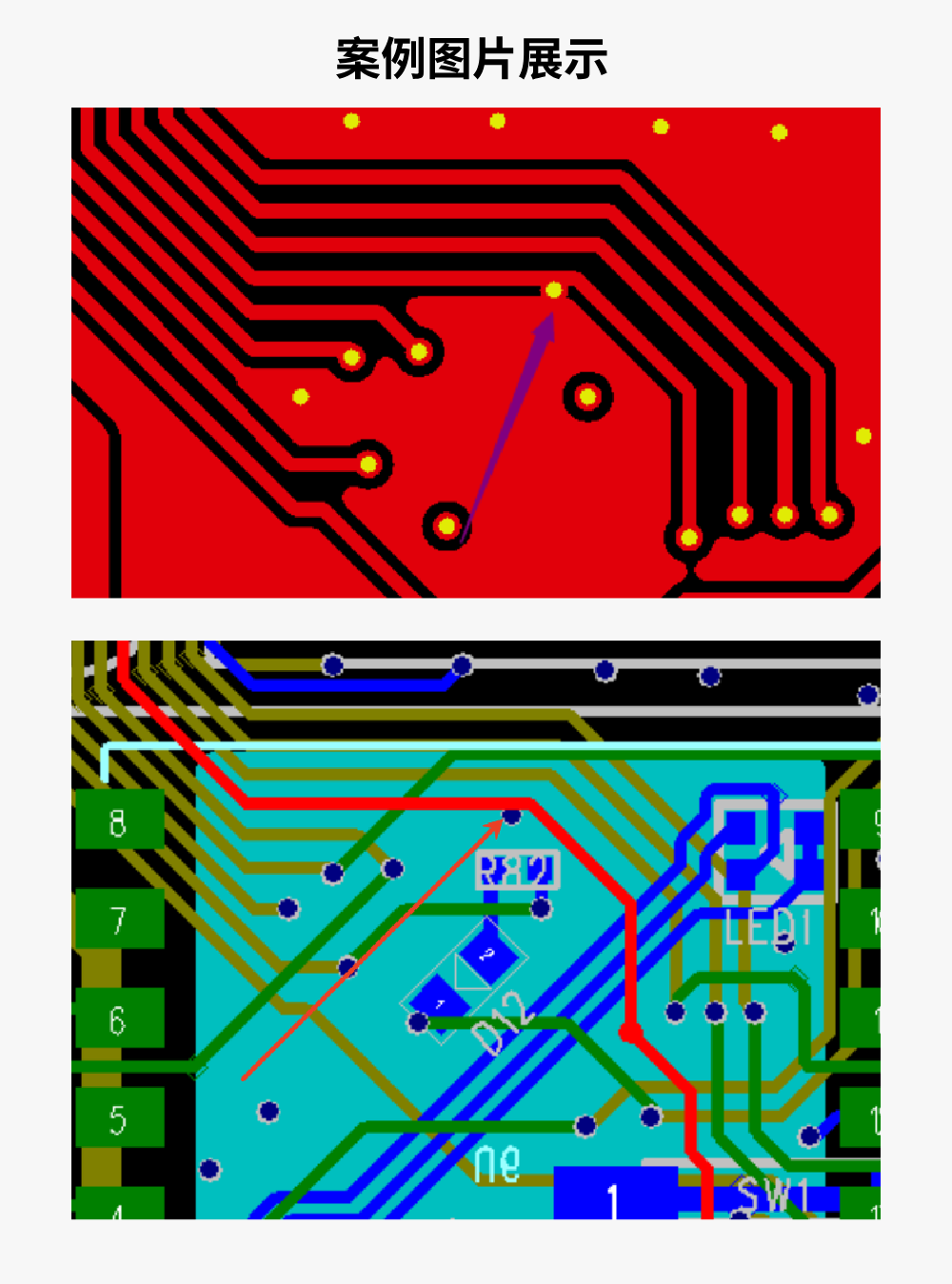

案例四:安全间距未设置

问题根源:过孔与导线、铜皮之间未遵循最小间距要求,设计阶段即存在物理连接风险,生产后直接形成短路。

案例二、三、四的发生均是没有开启DRC检查导致的。在Layout设计阶段,只要打开了DRC检查,并且设置了最小间距的参数,不同属性网络之间的信号,不管是线与线、孔与孔、孔与线、孔与铺铜之间均会报错,提醒修改,不同EDA设计软件可通过下述方式规避此类短路问题。

二、防患未然:PCB设计的防护盾

1、设计前期:工艺适配与规则设置

设计前需深入了解板厂工艺能力,获取最小最小线宽/线距、最小焊盘环宽、最小钻孔等关键尺寸,且保证设计规则必须优于或等于板厂的极限能力。

2、布线阶段:习惯规范与可视化检查

1)避免锐角布线:采用钝角(≥135°)或圆弧过渡设计,防止蚀刻过程中形成 “酸角” 残留铜渣,导致相邻线路短路。

2)科学使用泪滴:泪滴可强化连接,防止断裂;但在高密度区域,需警惕其与其他线路间距不足。

3)高亮网络检查:对电源网络(VCC、GND 等)、关键信号网络(时钟信号、差分信号等)启用高亮显示功能,逐层切换检查铜皮覆盖范围、走线路径及网络连接关系,直观排查非预期导通风险。

3、规则验证:DRC检查与DFM分析

1)DRC检查:

安全间距规则:覆盖所有网络对象组合(线-线、线-焊盘、焊盘-焊盘、孔-孔、孔-铜皮等),根据网络类型设置差异化最小间距值。

过孔专项规则:制定Via to Via间距规则,明确不同孔径过孔的最小间距要求,杜绝过孔重叠或过近导致的短路。

2)DFM分析

可使用DFM(可制造性分析)软件(如免费的华秋DFM)对设计源文件或者Gerber文件进行二次分析,这类工具检查角度不同,有时能发现新问题。

预防PCB设计中的短路问题,不能仅依赖最后一刻的DRC检查,而应建立一个贯穿始终的系统工程,将规则驱动、习惯约束与人工验证三者结合,尽可能的规避短路风险。