华秋PCB

高可靠多层板制造商

华秋SMT

高可靠一站式PCBA智造商

华秋商城

自营现货电子元器件商城

PCB Layout

高多层、高密度产品设计

钢网制造

专注高品质钢网制造

BOM配单

专业的一站式采购解决方案

华秋DFM

一键分析设计隐患

华秋认证

认证检测无可置疑

首页>技术中心>详情

很多时候,PCB走线中途会经过过孔、测试点焊盘、短的stub线等,都存在寄生电容,必然对信号造成影响。走线中途的电容对信号的影响要从发射端和接受端两个方面分析,对起点和终点都有影响。

首先按看一下对信号发射端的影响。当一个快速上升的阶跃信号到达电容时,电容快速充电,充电电流和信号电压上升快慢有关,充电电流公式为:I=C*dV/dt。电容量越大,充电电流越大,信号上升时间越快,dt越小,同样使充电电流越大。

我们知道,信号的反射与信号感受到的阻抗变化有关,因此为了分析,我们看一下,电容引起的阻抗变化。在电容开始充电的初期,阻抗表示为:

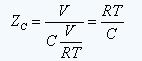

这里dV实际上是阶跃信号电压变化,dt为信号上升时间,电容阻抗公式变为:

从这个公式中,我们可以得到一个很重要的信息,当阶跃信号施加到电容两端的初期,电容的阻抗与信号上升时间和本身的电容量有关。

通常在电容充电初期,阻抗很小,小于走线的特性阻抗。信号在电容处发生负反射,这个负电压信号和原信号叠加,使得发射端的信号产生下冲,引起发射端信号的非单调性。

对于接收端,信号到达接收端后,发生正反射,反射回来的信号到达电容位置,那个样发生负反射,反射回接收端的负反射电压同样使接收端信号产生下冲。

为了使反射噪声小于电压摆幅的5%(这种情况对信号影响可以容忍),阻抗变化必须小于10%。那么电容阻抗应该控制在多少?电容的阻抗表现为一个并联阻抗,我们可以用并联阻抗公式和反射系数公式来确定它的范围。对于这种并联阻抗,我们希望电容阻抗越大越好。假设电容阻抗是PCB走线特性阻抗的k倍,根据并联阻抗公式得到电容处信号感受到的阻抗为:

阻抗变化率为:

即

,也就是说,根据这种理想的计算,电容的阻抗至少要是PCB特性阻抗的9倍以上。实际上,随着电容的充电,电容的阻抗不断增加,并不是一直保持最低阻抗,另外,每一个器件还会有寄生电感,使阻抗增加。因此这个9倍限制可以放宽。在下边的讨论中假设这个限制是5倍。

有了阻抗的指标,我们就可以确定能容忍多大的电容量。电路板上50欧姆特性阻抗很常见,我就用50欧姆来计算。

得出:

即在这种情况下,如果信号上升时间为1ns,那么电容量要小于4皮法。反之,如果电容量为4皮法,则信号上升时间最快为1ns,如果信号上升时间为0.5ns,这个4皮法的电容就会产生问题。

这里的计算只不过是为了说明电容的影响,实际电路中情况十分复杂,需要考虑的因素更多,因此这里计算是否精确没有实际意义。关键是要通过这种计算理解电容是如何影响信号的。我们对电路板上每一个因素的影响都有一个感性认识后,就能为设计提供必要的指导,出现问题就知道如何去分析。精确的评估需要用软件来仿真。

总结:

1 PCB走线中途容性负载使发射端信号产生下冲,接收端信号也会产生下冲。

2 能容忍的电容量和信号上升时间有关,信号上升时间越快,能容忍的电容量越小。

(作者:于争博士)

**********************************************************************

更多内容:

信号完整性(二):接收端容性负载的反射

信号完整性(三):PCB走线宽度变化产生的反射

信号完整性(四):信号振铃是怎么产生的

信号完整性(五):信号反射

信号完整性(六):多长的走线才是传输线

上一篇:PCB差分走线的阻抗控制技术(二)

下一篇:信号完整性(二):接收端容性负载的反射

自定义数量数量需为50的倍数,且大于10㎡

近期更新

查看全部>

新闻中心

扫描二维码咨询客户经理

关注华秋电路官方微信

实时查看最新订单进度

联系我们:

工作时间:

很多时候,PCB走线中途会经过过孔、测试点焊盘、短的stub线等,都存在寄生电容,必然对信号造成影响。走线中途的电容对信号的影响要从发射端和接受端两个方面分析,对起点和终点都有影响。

首先按看一下对信号发射端的影响。当一个快速上升的阶跃信号到达电容时,电容快速充电,充电电流和信号电压上升快慢有关,充电电流公式为:I=C*dV/dt。电容量越大,充电电流越大,信号上升时间越快,dt越小,同样使充电电流越大。

我们知道,信号的反射与信号感受到的阻抗变化有关,因此为了分析,我们看一下,电容引起的阻抗变化。在电容开始充电的初期,阻抗表示为:

这里dV实际上是阶跃信号电压变化,dt为信号上升时间,电容阻抗公式变为:

从这个公式中,我们可以得到一个很重要的信息,当阶跃信号施加到电容两端的初期,电容的阻抗与信号上升时间和本身的电容量有关。

通常在电容充电初期,阻抗很小,小于走线的特性阻抗。信号在电容处发生负反射,这个负电压信号和原信号叠加,使得发射端的信号产生下冲,引起发射端信号的非单调性。

对于接收端,信号到达接收端后,发生正反射,反射回来的信号到达电容位置,那个样发生负反射,反射回接收端的负反射电压同样使接收端信号产生下冲。

为了使反射噪声小于电压摆幅的5%(这种情况对信号影响可以容忍),阻抗变化必须小于10%。那么电容阻抗应该控制在多少?电容的阻抗表现为一个并联阻抗,我们可以用并联阻抗公式和反射系数公式来确定它的范围。对于这种并联阻抗,我们希望电容阻抗越大越好。假设电容阻抗是PCB走线特性阻抗的k倍,根据并联阻抗公式得到电容处信号感受到的阻抗为:

阻抗变化率为:

即

有了阻抗的指标,我们就可以确定能容忍多大的电容量。电路板上50欧姆特性阻抗很常见,我就用50欧姆来计算。

得出:

即在这种情况下,如果信号上升时间为1ns,那么电容量要小于4皮法。反之,如果电容量为4皮法,则信号上升时间最快为1ns,如果信号上升时间为0.5ns,这个4皮法的电容就会产生问题。

这里的计算只不过是为了说明电容的影响,实际电路中情况十分复杂,需要考虑的因素更多,因此这里计算是否精确没有实际意义。关键是要通过这种计算理解电容是如何影响信号的。我们对电路板上每一个因素的影响都有一个感性认识后,就能为设计提供必要的指导,出现问题就知道如何去分析。精确的评估需要用软件来仿真。

总结:

1 PCB走线中途容性负载使发射端信号产生下冲,接收端信号也会产生下冲。

2 能容忍的电容量和信号上升时间有关,信号上升时间越快,能容忍的电容量越小。

(作者:于争博士)

**********************************************************************

更多内容:

信号完整性(二):接收端容性负载的反射

信号完整性(三):PCB走线宽度变化产生的反射

信号完整性(四):信号振铃是怎么产生的

信号完整性(五):信号反射

信号完整性(六):多长的走线才是传输线

上一篇:PCB差分走线的阻抗控制技术(二)

下一篇:信号完整性(二):接收端容性负载的反射