高速电路传输线效应分析与处理随着系统设计复杂性和集成度的大规模提高,电子系统设计师们正在从事100MHZ以上的电路设计,总线的工作频率也已经达到或者超过50MHZ,有一大部分甚至超过100MHZ。目前约80% 的设计的时钟频率超过50MHz,将近50% 以上的设计主频超过120MHz,有20%甚至超过500M...

高速电路传输线效应分析与处理随着系统设计复杂性和集成度的大规模提高,电子系统设计师们正在从事100MHZ以上的电路设计,总线的工作频率也已经达到或者超过50MHZ,有一大部分甚至超过100MHZ。目前约80% 的设计的时钟频率超过50MHz,将近50% 以上的设计主频超过120MHz,有20%甚至超过500M... 2014-09-23

2014-09-23 12047

12047 PCB工艺设计规范规范产品的 PCB 工艺设计,规定 PCB 工艺设计的相关参数,使得 PCB 的设计满足可生产性、可测试性、安规、EMC、EMI 等的技术规范要求,在产品设计过程中构建产品的工艺、技术、质量、成本优势...

PCB工艺设计规范规范产品的 PCB 工艺设计,规定 PCB 工艺设计的相关参数,使得 PCB 的设计满足可生产性、可测试性、安规、EMC、EMI 等的技术规范要求,在产品设计过程中构建产品的工艺、技术、质量、成本优势... 2014-09-18

2014-09-18 21558

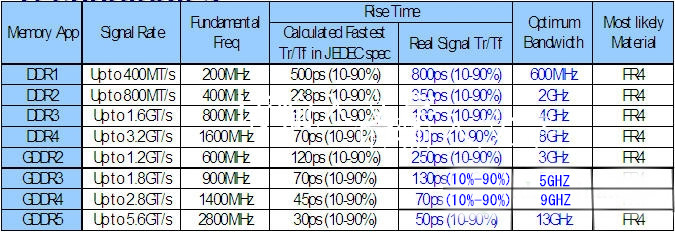

21558 DDR3总线信号完整性测试需要关注4点DDR总线需要测试时钟、命令/地址、数据等,数据测试是难点,而关键参数是建立时间和保持时间,所以需要对读写信号进行分离,分离后分别测试读和写信号的建立时间和保持时间。

DDR3总线信号完整性测试需要关注4点DDR总线需要测试时钟、命令/地址、数据等,数据测试是难点,而关键参数是建立时间和保持时间,所以需要对读写信号进行分离,分离后分别测试读和写信号的建立时间和保持时间。 2014-09-16

2014-09-16 9145

9145 Protel99se信号完整性的最新应用缓冲模型可以具体到引脚,批量信号分析结果比用默认模型精确得多;可以做到反射分析中过冲和下冲的批量准确分析,在信号完整性界面中还可以做比较准确的单个串扰分析和付立叶展开的频域分析,它可以确定信号中有害的EMI谐波分量...

Protel99se信号完整性的最新应用缓冲模型可以具体到引脚,批量信号分析结果比用默认模型精确得多;可以做到反射分析中过冲和下冲的批量准确分析,在信号完整性界面中还可以做比较准确的单个串扰分析和付立叶展开的频域分析,它可以确定信号中有害的EMI谐波分量... 2014-09-16

2014-09-16 7946

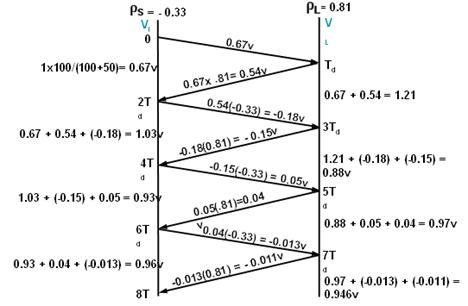

7946 信号完整性(四):信号振铃是怎么产生的信号的反射可能会引起振铃现象,那么信号振铃是怎么产生的呢?信号在驱动端和远端负载之间多次反射,其结果就是信号振铃。大多数芯片的输出阻抗都很低,如果输出阻抗小于PCB走线的特性阻抗,那么在没有源端端接的情况下,必然产生信号振铃...

信号完整性(四):信号振铃是怎么产生的信号的反射可能会引起振铃现象,那么信号振铃是怎么产生的呢?信号在驱动端和远端负载之间多次反射,其结果就是信号振铃。大多数芯片的输出阻抗都很低,如果输出阻抗小于PCB走线的特性阻抗,那么在没有源端端接的情况下,必然产生信号振铃... 2014-09-12

2014-09-12 11845

11845